# 2.69 inch AMOLED Display Series

Dalian Good Display Co., Ltd.

# **Product Specifications**

| Customer    | Standard             |

|-------------|----------------------|

| Description | 2.69" AMOLED DISPLAY |

| Model Name  | GD0J0269C01-T        |

| Date        | 2023/04/14           |

| Revision    | 1.0                  |

| D                     | esign Engineerin | g   |  |  |  |

|-----------------------|------------------|-----|--|--|--|

| Approval Check Design |                  |     |  |  |  |

| 宝刘<br>印玉              | 燕修印凤             | 之吴良 |  |  |  |

No.18, Zhonghua West ST, Ganjingzi DST, Dalian, CHINA

Tel: +86-411-84619565

Email: info@good-display.com

Website: www.good-display.com

# Content

| No. | Items                           | Page |

|-----|---------------------------------|------|

| 1   | General Description             | 4    |

| 2   | Mechanical Specification        | 6    |

| 3   | Absolute Maximum Ratings        | 6    |

| 4   | Electrical Characteristics      | 6    |

| 5   | Electro-optical Characteristics | 7    |

| 6   | FPC Pin Assignment              | 9    |

| 7   | AC Characteristics              | 10   |

| 8   | Recommended Operating Sequence  | 18   |

| 9   | Outline Information             | 21   |

| 10  | Reliability Test                | 27   |

| 11  | Handling Precautions            | 27   |

| 12  | Packing Specification           | 30   |

### 1. General Description 1.1 Introduction

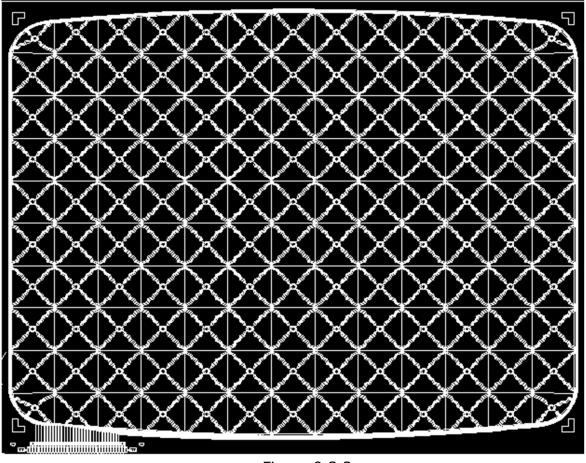

2.69" MDS is a color active matrix AMOLED module using Low Temperature Poly-silicon TFT's (Thin Film Transistors) as active switching devices. This module has a 2.69inch diagonally measured active area with 800RGBx600 resolutions (800horizontal by 600vertical pixel arrays). Each pixel is divided into RED, GREEN, BLUE dots which are arranged in vertical stripe and this module can display 16.7M colors.

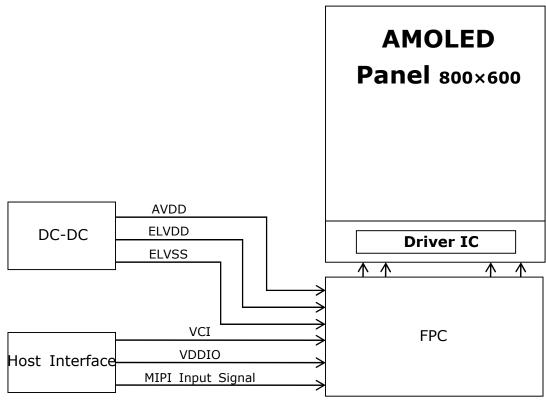

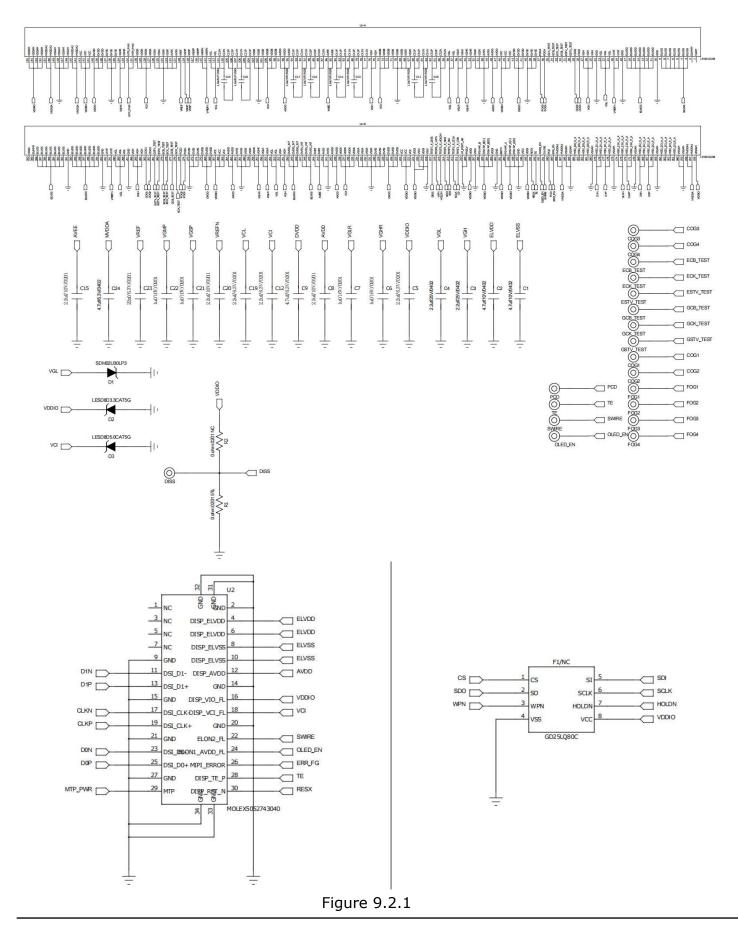

Figure 1.1

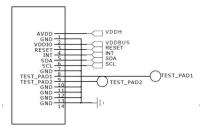

### 1.2 Driver IC Block Diagram

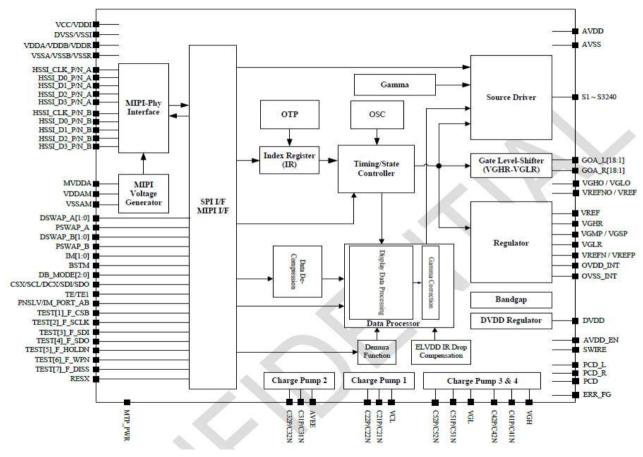

Figure 1.2

# 1.3 Features

- 1) Display Colors : 16.7M

- 2) Display Format : 2.69" Pentile RGB : 800×600

- 3) Interface : DSI 2-lane

- 4) Driver IC : RM69700 (Raydium)

- 5) Touch IC : S3601(Synaptics)

- 6) Polarizer : Hard Coating Polarizer

# **1.4 Application**

Night-vision Device

# 2. Mechanical Specification

|                   | Table 2.1                                     |      |        |  |  |  |

|-------------------|-----------------------------------------------|------|--------|--|--|--|

| Item              | Specifications                                | Unit | Remark |  |  |  |

| Panel outline     | 56.6(W) × 47.25(H)×0.505(T)                   | mm   |        |  |  |  |

| Number of dots    | 1600(W) × Pentile × 600(H)                    | Dots |        |  |  |  |

| Active area       | 54.6(W) × 40.95(H)                            | mm   |        |  |  |  |

| Diagonal Inch     | 2.69                                          | inch |        |  |  |  |

| Pixel pitch       | 68.25(W) × 68.25(H)                           | um   |        |  |  |  |

| Pixel Arrangement | Pentile                                       |      |        |  |  |  |

| Weight            | 4.87±0.1                                      | g    |        |  |  |  |

| Glass Thickness   | 0.20 (LTPS glass without PF)<br>0.305 (Encap) | mm   |        |  |  |  |

# 3. Absolute Maximum Ratings

|                       | Table 3.1 |      |      |      |      |  |  |

|-----------------------|-----------|------|------|------|------|--|--|

| Item                  | Symbol    | Min. | Max. | Unit | Note |  |  |

| I/O Voltage           | VDDIO     | -    | 6.6  | V    |      |  |  |

| Operation Voltage     | VCI       | -    | 6.6  | V    |      |  |  |

|                       | ELVDD     | 4.6  | -    | V    |      |  |  |

| EL Driving Voltage    | ELVSS     | -3   | -    | V    |      |  |  |

| Supply voltage        | TSP_VDD   | -0.3 | 3.6  | V    |      |  |  |

| (TSP)                 | IOVDD     | -0.3 | 3.6  | V    |      |  |  |

| Operating temperature | Topr      | -40  | 85   | °C   | -    |  |  |

| Storage temperature   | Tstg      | -55  | 125  | С°   | -    |  |  |

# 4. Electrical Characteristics

Test Condition: Temp=25±2℃

Table 4.1

| Item          | Min. | Тур. | Max. | Unit | Remark     |

|---------------|------|------|------|------|------------|

| Logic Power   | 1.62 | 1.8  | 1.98 | V    |            |

| ELVDD         | 4.6  | 4.6  | 4.6  | V    |            |

| ELVSS         | -3   | -2.0 | -1.4 | V    | 100mV Step |

| AVDD          | 6.8  | 6.8  | 7.8  | V    |            |

| VCI           | 2.7  | 3.0  | 3.6  | V    |            |

| VDDIO         | 1.62 | 1.8  | 1.98 | V    |            |

| Logic Current | 20   | 23   | 26   | mA   |            |

| Freq          | -    | 50   | -    | Hz   |            |

| VGH           | 5.7  | 6    | 7    | V    |            |

| VGL           | -7   | -6   | -5.4 | V    |            |

| VGH           | 5.7  | 6    | 7    | V    |            |

Notes :

- 1. VGH is TFT Gate operating voltage.

- 2. VGL is TFT Gate operating voltage.

- 3. The value is just the reference value. The customer can optimize the setting value by the different D-IC.

- 4. RM69700, DualRam.

# 5. Electro-optical Characteristics

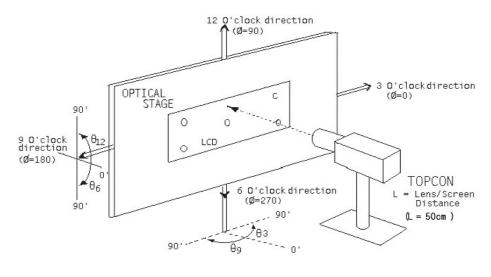

The test of optical specifications shall be measured in a dark room (ambient luminance  $\leq$ 1lux and temperature = 25±2°C) with the equipment of Luminance meter. We refer to  $\theta$ ,  $\emptyset = 0^{\circ}$  (= $\theta_3$ ) as the 3 o'clock direction (the "right"),  $\theta$ ,  $\emptyset = 90^{\circ}$  (=  $\theta_{12}$ ) as the 12 o'clock direction ("upward"),  $\theta$ ,  $\emptyset$ =180° (=  $\theta$ 9) as the 9 o'clock direction ("left") and  $\theta$ ,  $\emptyset$ =270°  $(= \theta_6)$  as the 6 o'clock direction ("bottom"). While scanning  $\theta$  and/or  $\emptyset$ , the center of the measuring spot on the Display surface shall stay.

| lte        | m                     | Symbol          | Condition           | Min.          | Тур.                                    | Max.   | Unit        | Note  |

|------------|-----------------------|-----------------|---------------------|---------------|-----------------------------------------|--------|-------------|-------|

|            |                       | θ <sub>3</sub>  |                     |               | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |        |             |       |

| Viewing    | Horizontal            | θ <sub>9</sub>  | CR ratio≥1600       | 00            |                                         |        | 0           | Neted |

| Angle      | Vertical              | $\theta_6$      |                     | 80            | -                                       | -      |             | Note1 |

|            | Vertical              | θ <sub>12</sub> |                     |               |                                         |        |             |       |

| I          | Brightness            |                 | θ=0° At Center      | 380           | 420                                     | 460    | nit         |       |

| Contra     | st ratio              | CR              | θ=0°                | 100,000:<br>1 | -                                       | -      | -           | Note2 |

| Brightness | Uniformity            | LRU             | W255                | 75            | 80                                      | -      | %           | Note3 |

|            | White                 | X <sub>W</sub>  |                     | 0.2790        | 0.2990                                  | 0.3190 |             |       |

|            |                       | Уw              | θ=0°                | 0.2949        | 0.3149                                  | 0.3349 | CIE<br>1931 |       |

|            | Red                   | XR              |                     | 0.660         | 0.680                                   | 0.700  |             | Note4 |

| Color of   |                       | УR              |                     | 0.300         | 0.320                                   | 0.340  |             |       |

| CIE        | Green                 | XG              | 0-0                 | 0.215         | 0.245                                   | 0.275  |             | NOLC4 |

| coordinate | Green                 | УG              |                     | 0.685         | 0.715                                   | 0.745  |             |       |

|            | Blue                  | ХB              |                     | 0.121         | 0.141                                   | 0.161  |             |       |

|            | Dide                  | Ув              |                     | 0.025         | 0.045                                   | 0.065  |             |       |

| C          | olor Gamut            |                 | θ=0° vs. NTSC       | -             | 100                                     | -      | %           |       |

| Re         | sponse Time           |                 | G To G              |               |                                         | 2      | ms          |       |

| Cro        | oss Talk(5nit)        |                 | Window: black       |               | 3.5                                     | 5      | %           | Note5 |

| Cross Ta   | Cross Talk(100nit&420 |                 | Background: gray127 | -             | -                                       | 3      | 70          | NOLES |

|            | Colorshift            |                 | W255                | 3(30°)        | 4(45°)                                  | 5(60°) | JNCD        |       |

|            | Gamma                 |                 | Subsection Control  | 1.9           | 2.2                                     | 2.5    | -           | -     |

| Life time  | LT93 I                | B10             | Room temperature    | -             | 240                                     | -      | hrs         |       |

|            | LT93 I                | B10             | <b>50</b> ℃         |               | 72                                      |        | hrs         |       |

Table 5.1

Notes :

1. Viewing angle is the angle at which the contrast ratio is greater than 1600:1. The viewing angles are determined for the horizontal or 3, 9 o'clock direction and the vertical or 6, 12 o'clock direction with respect to the optical axis which is normal to the panel surface (see Figure 3).

7/30

Figure 5.1

2. Contrast measurements shall be made at viewing angle of  $\theta = 0^{\circ}$  and at the center of the panel surface. Luminance shall be measured with all pixels in the view field set first to white, then to the dark (black) state. (see Figure 3) Luminance Contrast Ratio (CR) is defined mathematically.

$CR = \frac{Luminance when displaying a white raster}{Luminance when displaying a black raster}$

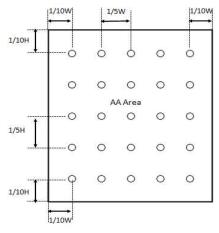

3. Uniformity. LRU Refer to figure as below:

Figure 5.2

Uniformity measurements shall be made at $\theta = 0^{\circ}$  and at the different points of the panel surface. Luminance shall be measured with all pixels in the view field set to W/R/G/B at 255 Gary level, respectively. Luminance uniformity=Lmin/Lmax ×100%

- 4. The color chromaticity coordinates specified in Table 4 shall be calculated from the spectral data measured with all pixels first in red, green, blue and white. Measurements shall be made at the center of the panel.

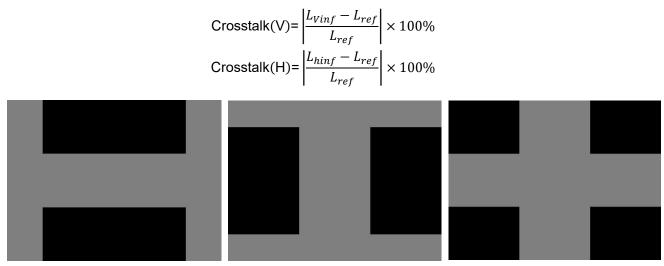

- 5. Crosstalk measurement shall be done at the center of the different pattern and the result shall be calculated as follow formula.

- a. measure luminance at the center.

- b. calculate cross talk as below equation:

Figure 5.3

# 6. FPC Pin Assignment

Main FPC assignment- AMOLED Panel Input/output Signal Interface. Recommended connector: Molex5052743040

| No. | Name    | No. | Name    |

|-----|---------|-----|---------|

| 1   | NC      | 2   | GND     |

| 3   | NC      | 4   | ELVDD   |

| 5   | NC      | 6   | ELVDD   |

| 7   | NC      | 8   | ELVSS   |

| 9   | GND     | 10  | ELVSS   |

| 11  | D1N     | 12  | AVDD    |

| 13  | D1P     | 14  | GND     |

| 15  | GND     | 16  | VDDIO   |

| 17  | CLKN    | 18  | VCI     |

| 19  | CLKP    | 20  | GND     |

| 21  | GND     | 22  | SWIRE   |

| 23  | D0N     | 24  | OLED_EN |

| 25  | D0P     | 26  | ERR_FG  |

| 27  | GND     | 28  | TE      |

| 29  | MTP_PWR | 30  | RESX    |

Table 6.1

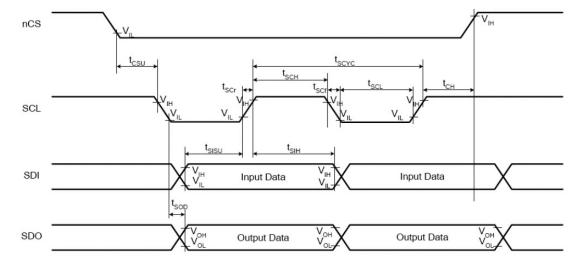

# 7. AC Characteristics 7.1 Serial Interface Characteristics

Figure 7.1

#### Table 7.1

| Signal              | Symbol            | Parameter                     | MIN | MAX | Unit |

|---------------------|-------------------|-------------------------------|-----|-----|------|

|                     | T <sub>SCYC</sub> | Clock cycle (Write)           | 100 | -   | ns   |

|                     | T <sub>SCYC</sub> | Clock cycle (Read)            | 300 | -   | ns   |

|                     | T <sub>SCH</sub>  | Clock "H" pulse width (Write) | 40  | -   | ns   |

| SCL                 | T <sub>SCH</sub>  | Clock "H" pulse width (Read)  | 140 | -   | ns   |

| SUL                 | T <sub>SCL</sub>  | Clock "L" pulse width (Write) | 40  | -   | ns   |

|                     | T <sub>SCL</sub>  | Clock "L" pulse width (Read)  | 140 | -   | ns   |

|                     | T <sub>SCr</sub>  | Clock rise time               | -   | 5   | ns   |

| T <sub>SCf</sub>    |                   | Clock fall time               | -   | 5   | ns   |

| 500                 | T <sub>CSU</sub>  | Chip select setup time        | 20  | -   | ns   |

| nCS T <sub>CH</sub> |                   | Chip select hold time         | 50  | -   | ns   |

| SDI                 | T <sub>SISU</sub> | Data input setup time         | 20  | -   | ns   |

|                     | T <sub>SIH</sub>  | Data input hold time          | 20  | -   | ns   |

| 000                 | T <sub>SOD</sub>  | Data output setup time        | -   | 120 | ns   |

| SDO                 | T <sub>SOH</sub>  | Data output hold time         | 5   | -   | ns   |

#### Notes:

1.Logic high and low levels are specified as 20% and 80% of VDDI for Input signals. 2.Ta =  $-40^{\circ}$ C to 85°C, VDDI=1.62V to 1.98V, VCI=2.5V to 3.6V, GND=0V

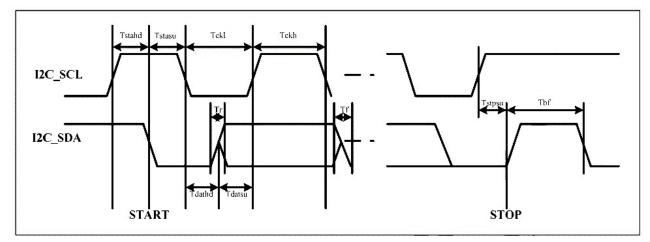

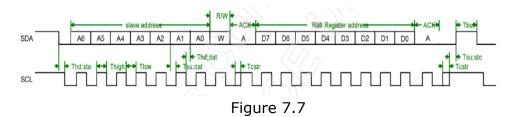

# 7.2 I2C Bus Timing Characteristics

|         |             | Table 7.2         |      |     |      |

|---------|-------------|-------------------|------|-----|------|

| Signal  | Symbol      | Parameter         | MIN  | MAX | Unit |

|         | Tckl + Tckh | Operate frequency | -    | 400 | ns   |

| I2C_SCL | Tckl        | CLK low           | 1300 | -   | ns   |

|         | Tckh        | CLK high          | 600  | -   | ns   |

|         | Tr          | Data rising time  | -    | 300 | ns   |

|         | Tf          | Data falling time | -    | 300 | ns   |

|         | Tdathd      | Data hold time    | 0    | 900 | ns   |

| I2C SDA | Tdatsu      | Data setup time   | 100  | -   | ns   |

| 120_3DA | Tstahd      | Start hold time   | 600  | -   | ns   |

|         | Tstasu      | Start setup time  | 600  | -   | ns   |

|         | Tstpsu      | Stop setup time   | 600  | -   | ns   |

|         | Tbf         | Bus free time     | 1300 | -   | ns   |

### Table 7.2

#### Notes:

- 1. Logic high and low levels are specified as 20% and 80% of IOVCC for input signals.

- 2. Ta=-40 to 85°C, IOVCC=1.62V to 1.98V, VCI=2.5V to 3.6V, GND=0V.

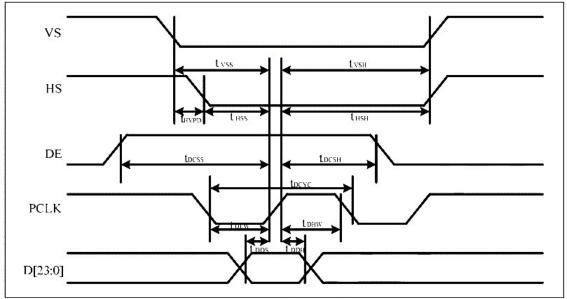

# 7.3 RGB Interface Characteristics

Figure 7.3

| Signal  | Symbol            | Parameter             | MIN | TYP | MAX | Unit |

|---------|-------------------|-----------------------|-----|-----|-----|------|

|         | t <sub>DCYC</sub> | PCLK cycle time       | 15  | -   | -   | ns   |

| PCLK    | t <sub>DLW</sub>  | PCLK low pulse width  | 7   | -   | -   | ns   |

|         | t <sub>DHW</sub>  | PCLK high pulse width | 7   | -   | -   | ns   |

| VS      | t∨ss              | VS setup time         | 3   | -   | -   | ns   |

| V3      | t <sub>∨sн</sub>  | VS hold time          | 3   | -   | -   | ns   |

|         | t <sub>HSS</sub>  | HS setup time         | 3   | -   | -   | ns   |

| HS      | t <sub>HSH</sub>  | HS hold time          | 3   | -   | -   | ns   |

|         | t <sub>HVPD</sub> | HS to VS falling edge | 400 | -   | -   | ns   |

| DE      | t <sub>DCSS</sub> | DE setup time         | 3   | -   | -   | ns   |

|         | t <sub>DCSH</sub> | DE hold time          | 3   | -   | -   | ns   |

| D[00.0] | t <sub>DDS</sub>  | Data setup time       | 3   | -   | -   | ns   |

| D[23:0] | t <sub>DDH</sub>  | Data hold time        | 3   | -   | -   | ns   |

Notes:

- 1. Logic high and low levels are specified as 20% and 80% of IOVCC for input signals.

- 2. Ta=-40 to  $85^{\circ}$ C, IOVCC=1.62V to 1.98V, VCI=2.5V to 3.6V, GND=0V.

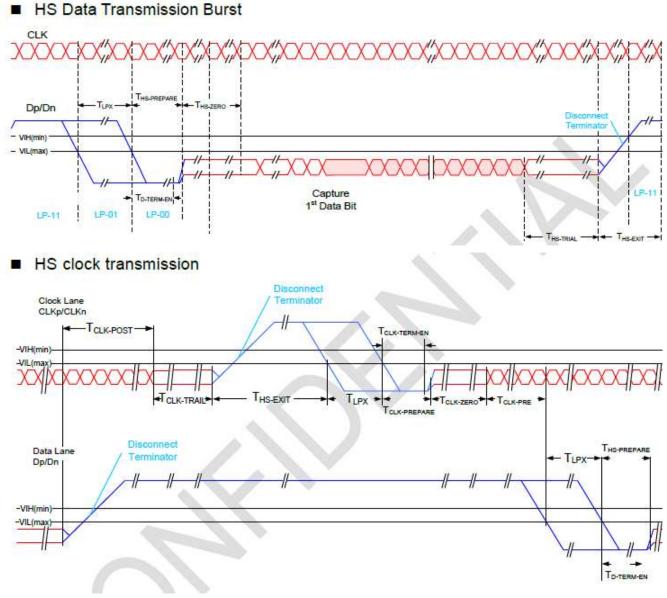

# 7.4 DSI Timing Characteristics

Figure 7.4

| Parameter                | Description                                                     | MIN              | MAX | Unit |

|--------------------------|-----------------------------------------------------------------|------------------|-----|------|

|                          | Time that the transmitter continues to send HS clock            |                  |     |      |

| <b>-</b>                 | after the last associated Data Lane has transitioned            | 60pg ( 50 x l II |     | 20   |

| T <sub>CLK-POST</sub>    | to LP Mode. Interval is defined as the period from              | 60ns+52×UI       |     | ns   |

|                          | the end of $T_{HS-TRIAL}$ to the beginning of $T_{CLK-TRAIL}$ . |                  |     |      |

|                          | Time that the transmitter drives the HS-0 state after           |                  |     |      |

| T <sub>CLK-TRAIL</sub>   | the last payload clock bit of a HS transmission                 | 60               |     | ns   |

|                          | burst.                                                          |                  |     |      |

| -                        | Time that the transmitter drives LP-11 following a              | 200              |     | 20   |

| T <sub>HS-EXIT</sub>     | HS burst.                                                       | 300              |     | ns   |

| T <sub>CLK-TERM-EN</sub> | Time for the Clock Lane receiver to enable the HS               | Time for Dn to   | 38  | ns   |

|                          | line termination, Starting from the time point when                | reach V <sub>TERM-EN</sub> |           |    |

|--------------------------|--------------------------------------------------------------------|----------------------------|-----------|----|

|                          | Dn crosses V <sub>IL, MAX</sub> .                                  |                            |           |    |

|                          | Time that the transmitter drives the Clock Lane LP-                |                            |           |    |

| T <sub>CLK-PREPARE</sub> | 00 Line state immediately before the HS-0 Line                     | 38                         | 95        | ns |

|                          | state starting the HS transmission.                                |                            |           |    |

|                          | Time that the HS clock shall be driven by the                      |                            |           |    |

| T <sub>CLK-PRE</sub>     | transmitter prior to any associated Data Lane                      | 8                          |           | UI |

|                          | beginning the transition from LP to HS mode.                       |                            |           |    |

| T <sub>CLK-PREPARE</sub> | T <sub>CLK-PREPARE</sub> + time that the transmitter drives the    | 200                        |           | 20 |

| +T <sub>CLK-ZERO</sub>   | HS-0 state prior to starting the Clock.                            | 300                        |           | ns |

|                          | Time for the Data Lane receiver to enable the HS                   | Time for Dr. to            |           |    |

| T <sub>D-TERM-EN</sub>   | line termination, starting from the time point when                | Time for Dn to             | 35ns+4×UI | ns |

|                          | Dn crosses V <sub>IL, MAX</sub> .                                  | reach $V_{\text{TERM-EN}}$ |           |    |

|                          | Time that the transmitter drives the Data Lane LP-                 |                            |           |    |

| T <sub>HS-PREPARE</sub>  | 00 Line state immediately before the HS-0 Line                     | 40ns+4×UI                  | 85ns+6×UI | ns |

|                          | state starting the HS transmission.                                |                            |           |    |

| T <sub>HS-PREPARE</sub>  | T <sub>HS-PREPARE</sub> + time that the transmitter drives the HS- | 145ns+10×UI                |           | 20 |

| +T <sub>HS-ZERO</sub>    | 0 state prior to transmitting the Sync sequence.                   | 1450S+10×01                |           | ns |

|                          | Time that the transmitter drives the flipped                       |                            |           |    |

| T <sub>HS-TRIAL</sub>    | differential state after last payload data bit of a HS             | 60ns+4×UI                  |           | ns |

|                          | transmission burst.                                                |                            |           |    |

| TAB-SKEW                 | Timing Skew between Port A and Port B                              |                            | 100       |    |

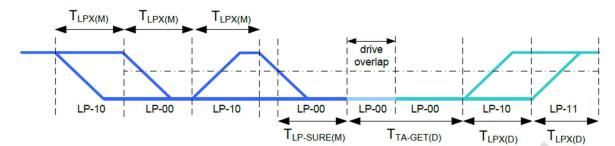

#### Bus Turnaround Procedure (From MPU to display module)

Bus turnaround (BAT) timing

### Table 7.5

■ Timing Specifications for Low Power Transmission:

| Parameter               | Description                                                                                                                              | Min                 | Тур                   | Max                   | Unit | Notes |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------|------|-------|

| T <sub>LPX(M)</sub>     | Transmitted length of any Low-Power state period of MCU to display module                                                                | 50                  |                       | 150                   | ns   | 1,2   |

| T <sub>TA-SURE(M)</sub> | Time that the display module waits after<br>the LP-10 state before transmitting the<br>Bridge state (LP-00) during a Link<br>Turnaround. | T <sub>LPX(M)</sub> |                       | 2*T <sub>LPX(M)</sub> | ns   | 2     |

| T <sub>LPX(D)</sub>     | Transmitted length of any Low-Power state period of display module to MCU                                                                | 50                  |                       | 150                   | ns   | 1,2   |

| T <sub>TA-GET(D)</sub>  | Time that the display module drives the Bridge state (LP-00) after accepting control during a Link Turnaround.                           |                     | 5*T <sub>LPX(D)</sub> |                       | ns   | 2     |

| T <sub>TA-GO(D)</sub>   | Time that the display module drives the<br>Bridge state (LP-00) before releasing<br>control during a Link Turnaround.                    |                     | 4*T <sub>LPX(D)</sub> |                       | ns   | 2     |

| T <sub>TA-SURE(D)</sub> | Time that the MPU waits after the LP-10 state before transmitting the Bridge state (LP-00) during a Link Turnaround.                     | T <sub>LPX(D)</sub> |                       | 2*T <sub>LPX(D)</sub> | ns   | 2     |

Notes:

1. TLPX is an internal state machine timing reference. Externally measured values may differ slightly from the specified values due to asymmetrical rise and fall times.

2. Transmitter-specific parameter

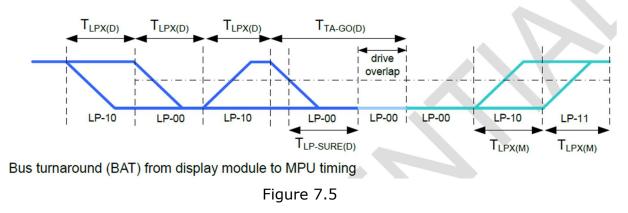

# 7.5 Reset Timing

Figure 7.6

| Reset timing @VDDI=1.62V to 1.98V, VSSA=DVSS=VSSI=0V, Ta=-40°C to 85°C |                       |     |     |     |                                                                                                                                                                              |      |  |  |

|------------------------------------------------------------------------|-----------------------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| Symbol                                                                 | Parameter             | MIN | TYP | MAX | Note                                                                                                                                                                         | Unit |  |  |

| t <sub>RESW</sub>                                                      | Reset low pulse width | 15  |     |     | <ol> <li>Shorter than 5us, Reset rejected</li> <li>Longer than 15μs, IC reset</li> <li>Between 5μs and 15μs, It depends on<br/>voltage and temperature condition.</li> </ol> | μs   |  |  |

|                                                                        | Depat complete time   | -   | -   | 10  | When reset applied at sleep-in mode                                                                                                                                          | ms   |  |  |

| t <sub>REST</sub>                                                      | Reset complete time   | -   | -   | 120 | When reset applied at sleep-out mode                                                                                                                                         | ms   |  |  |

Table 7.6 Reset timing @VDDI=1.62V to 1.98V, VSSA=DVSS=VSSI=0V, Ta=-40℃ to 85℃

# 7.6 Touch Panel I2C Timing Characteristics

| Deservator                                                                                         | Sumbal              |      | Standard Mod | е    |                        | Fast Mode |     |     |

|----------------------------------------------------------------------------------------------------|---------------------|------|--------------|------|------------------------|-----------|-----|-----|

| Parameter                                                                                          | Symbol              | Min  | Тур          | Max  | Min                    | Тур       | Max | Uni |

| SCL clock frequency                                                                                | f <sub>SCL</sub>    | 5-   | -            | 100  | -                      | -         | 400 | kHz |

| Clock stretch time                                                                                 | <sup>L</sup> CSTR   | -    | <25          | -    | -                      | <25       | -   | us  |

| Hold time (repeated) START<br>condition. After this period, the<br>first clock pulse is generated. | t <sub>hd;sta</sub> | 4.0  | -            | -    | 0.6                    | ).        | Z-  | us  |

| Low period of the SCL clock                                                                        | t <sub>LOW</sub>    | 4.7  | -            | -    | 9 (9.3                 | - AD      | -   | us  |

| High period of the SCL clock                                                                       | t <sub>HIGH</sub>   | 4.0  | -            | - 20 | 0.6                    | S.        | -   | us  |

| Setup time for repeated<br>START condition                                                         | t <sub>su;sta</sub> | 4.7  | -            | Ś    | 0.6                    | -         | -   | us  |

| Data hold time                                                                                     | thd;dat             | 0    | - 20         | Ø.   | O                      | -         | -   | us  |

| Data out valid time                                                                                | tvalid;dato         | -    | ja ja        | 3.45 |                        | -         | 0.9 | us  |

| Data setup time                                                                                    | t <sub>su;dat</sub> | 250  | 6            |      | 100                    | -         | -   | ns  |

| Rise time of SDA/SCL                                                                               | t <sub>R</sub>      | - (( | 1 2          | 1000 | 20 + 0.1C <sub>B</sub> | -         | 300 | ns  |

| Fall time of SDA/SCL                                                                               | t⊧                  | 20   | - 6          | 300  | 20 + 0.1C <sub>B</sub> | -         | 300 | ns  |

| Setup time for STOP condition                                                                      | tsu:sto             | 4.0  | 102          | 2.   | 0.6                    | -         | -   | us  |

| Bus free time between a<br>STOP and START condition                                                | t <sub>BUF</sub>    | 4.7  |              | -    | 1.3                    | -         | -   | us  |

| Capacitive load for each bus line                                                                  | CB                  | -~   | XS-          | 400  | -                      | -         | 400 | pF  |

Table 7.7

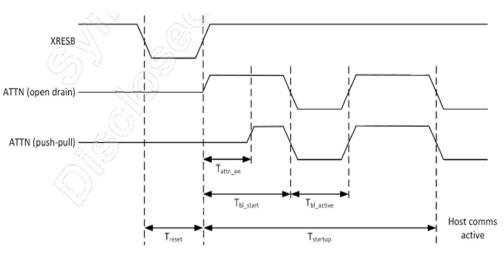

# 7.7 Touch Panel RESET Timing Characteristics

Figure 7.8

| Tabl | le | 7.8 |  |

|------|----|-----|--|

|      | -  |     |  |

| Power supply                               | Min   | Max | Unit |

|--------------------------------------------|-------|-----|------|

| T <sub>attn_en</sub>                       | 5     | 21  | ms   |

| Tpowerup                                   |       | 45  | ms   |

| T <sub>startup</sub>                       | 12 11 | 45  | ms   |

| Tbl_start (bootloader start)               |       | 30  | ms   |

| T <sub>bl_active</sub> (bootloader active) | - MO  | 15  | ms   |

| T <sub>reset</sub>                         | 100   | -   | ns   |

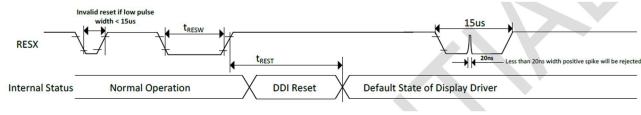

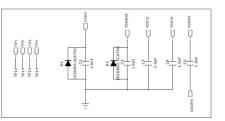

# 8. Recommended Operating Sequence

# 8.1 Display Power on/off Sequence

#### Power On sequence 96ms 10ms IC state OTP Reload unknown Reset Command Exe. Power-up sequence Display-On VDDI VCI TON2 Т3 т4 RESX Flash Reload Period Flash reload DISPON Initial setting SLPOUT MIPI I/F $\square$ LP-11 т6 T2 AVDD\_EN SWIRE **T7** Т9 Power Off sequence Display-On Blanking SLPIN Reset unknown IC state VDDI VCI RESX DISPOFF SLPIN MIPI I/F M T10 T11 T12 T13

#### Power Sequence and Generation

| Contral    | Value |      |            | 1.1  | Demanda                                           |

|------------|-------|------|------------|------|---------------------------------------------------|

| Symbol     | Min.  | Typ. | Max.       | Unit | Remark                                            |

| TON2       | 2     | · 4  | -          | ms   |                                                   |

| T2         | 1     | -    |            | ms   | MIPI stabilization time                           |

| T3         | 1     | -    | -          | ms   | Effective hardware reset period                   |

| T4         | 10    | 1    | -          | ms   | OTP reload time                                   |

| T6         | 0     |      | <b>F</b> 1 | ms   | Initial code input finish to SLPOUT command input |

| T7         | 84    | 96   | 4          | ms   | Normal power-up sequence                          |

| <b>T</b> 9 | 2     | 1.5  | . 5        | VS   | Display-On Blanking region                        |

| T10        | 2     |      | -          | VS   | Display-Off blanking region                       |

| T11        | 1     | -    |            | VS   | Blanking region                                   |

| T12        | 1     |      | -          | ms   | Effective hardware reset period                   |

| T13        | 2     | 121  | ÷ .,       | ms   | Power off period                                  |

| Timing       | Specification | of Power | On/Off Sequence |

|--------------|---------------|----------|-----------------|

| <br>1 mining | opeoincution  |          | on on ocquence  |

Notes:

VS means the time period of a complete display frame and is approximately 16ms if internal display timing is used.

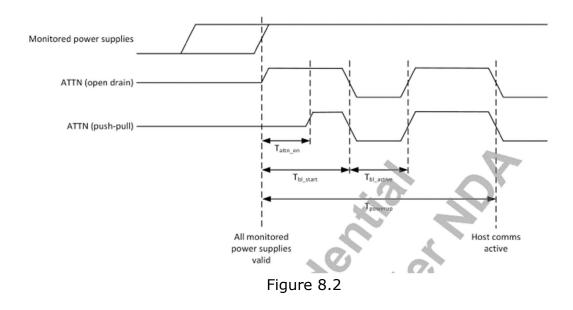

# 8.2 Touch Panel Power on Sequence

| Power supply                               | Min              | Max | Unit |

|--------------------------------------------|------------------|-----|------|

| T <sub>attn_en</sub>                       | 5                | 21  | ms   |

| Tpowerup                                   |                  | 45  | ms   |

| T <sub>startup</sub>                       | ( <u>7</u> 2) [[ | 45  | ms   |

| T <sub>bl_start</sub> (bootloader start)   |                  | 30  | ms   |

| T <sub>bl_active</sub> (bootloader active) | 0, - "0          | 15  | ms   |

| T <sub>reset</sub>                         | 100              | -   | ns   |

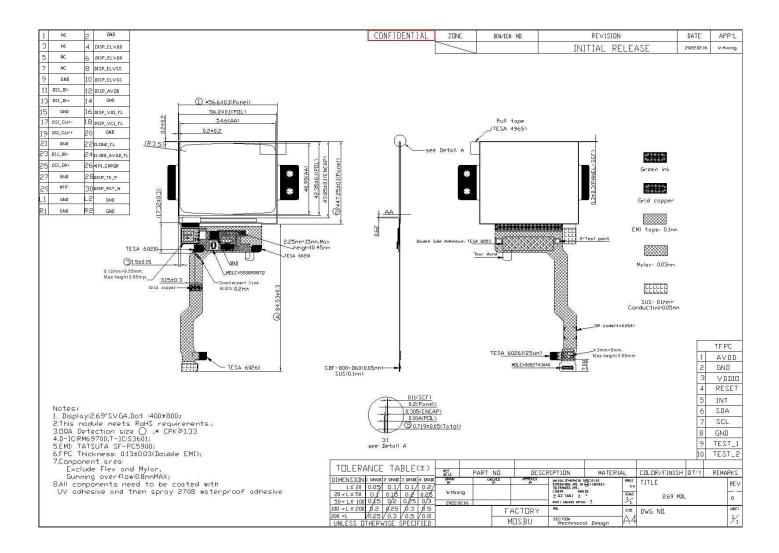

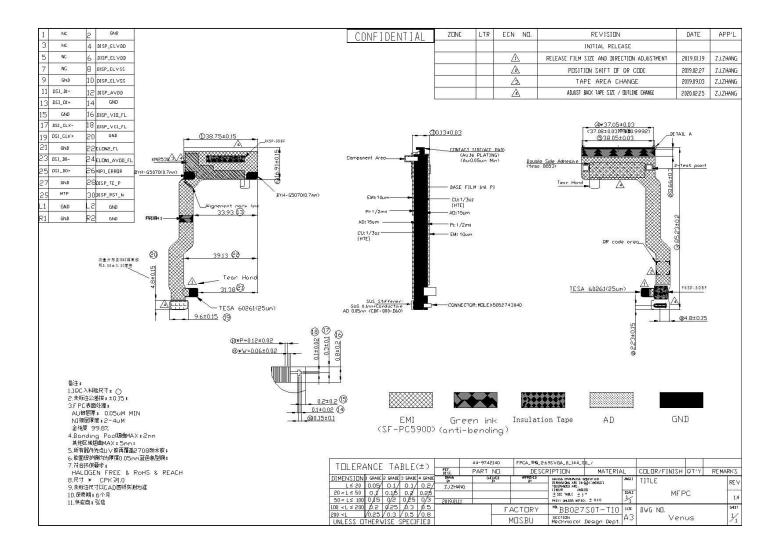

# **9.** Outline Information 9.1 Total Outline

Figure 9.1

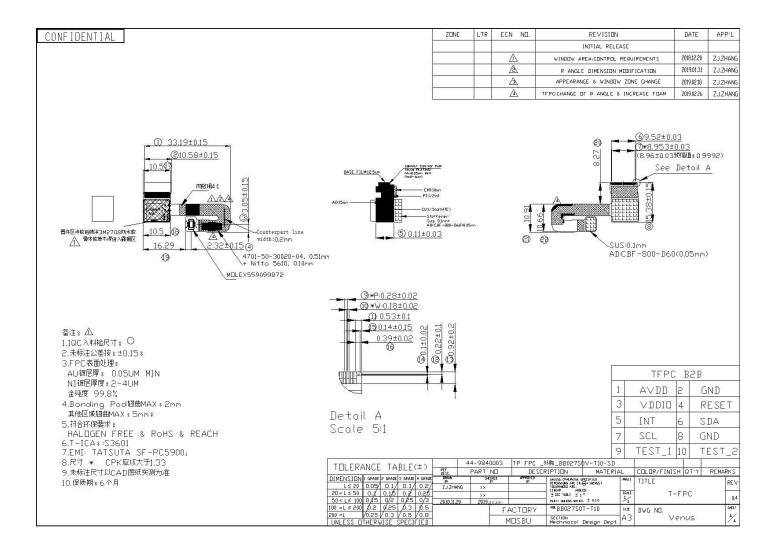

# 9.2 Main FPCB Drawing

# 9.2.1 Main FPC Schematic Diagram

# 9.2.2 Main FPC Electronic Part List

| Comment | Description | Designator    | Footprint                    | Quantity | Value      |

|---------|-------------|---------------|------------------------------|----------|------------|

| Сар     | Capacitor   | C16-17        | 0201                         | 2        | 1uF/10V    |

| Сар     | Capacitor   | C10-11 C13-14 | 0201                         | 4        | 1uF/16V    |

| Сар     | Capacitor   | C18,C25       | 0201                         | 2        | 1uF/6.3V   |

| Сар     | Capacitor   | C21-22        | 0201                         | 2        | 1uF/10V    |

| Сар     | Capacitor   | C6-7          | 0201                         | 2        | 1uF/16V    |

| Сар     | Capacitor   | C8,C15,C20    | 0201                         | 3        | 2.2uF/10V  |

| Сар     | Capacitor   | C5,C12,C19    | 0201                         | 3        | 2.2uF/6.3V |

| Сар     | Capacitor   | C23           | 0201                         | 1        | 22nF/6.3V  |

| Сар     | Capacitor   | C9            | 0201                         | 1        | 4.7uF/6.3V |

| Сар     | Capacitor   | C3-4          | 0402                         | 2        | 2.2uF/25V  |

| Cap     | Capacitor   | C1-2          | 0402                         | 2        | 4.7uF/10V  |

| Сар     | Capacitor   | C24           | 0402                         | 1        | 4.7uF/6.3V |

| Diode   | diode       | D1            | SDM02U30LP3                  | 1        |            |

| Diode   | diode       | D2/NC         | LESD8D5.0CT5G,LESD8D3.3CAT5G | 1        | NC         |

| Diode   | diode       | D3/NC         | LESD8D5.0CT5G,LESD8D5.0CAT5G | 1        | NC         |

| Res1    | Resistor    | R1            | 0201                         | 1        | 0ohm/5%    |

| Res1    | Resistor    | R2/NC         | 0201                         | 1        | 0ohm/5%    |

| u2      | Connector   |               | MOLEX5052743040              | 1        |            |

| flash   |             | F1/NC         | GD25LQ80C                    | 0        | NC         |

#### Table 9.2

## 9.2.3 Main FPC Placement

Figure 9.2.3 PVT

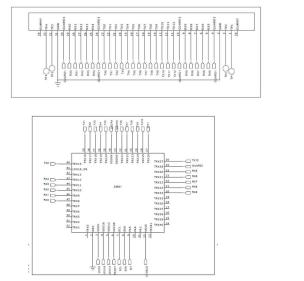

# 9.3 Touch Sensor Drawing 9.3.1 TSP FPC Schematic Diagram

Figure 9.3.1

### 9.3.2 TSP FPC Electronic Part List

Figure 9.3.2

| TFPC    |                                    |       |                |          |          |  |  |

|---------|------------------------------------|-------|----------------|----------|----------|--|--|

| Comment | mment Description Designator Footp |       | Footprint      | Quantity | Value    |  |  |

| Сар     | Capacitor                          | C3/C4 | 0402           | 2        | 1uF/6.3V |  |  |

| Сар     | Capacitor                          | C2    | 0402           | 1        | 1uF/6.3V |  |  |

| Сар     | Capacitor                          | C1/C5 | 0402           | 2        | 1uF/10V  |  |  |

| Diode   | Diode                              | D1/NC | LESD8D5.0CAT5G | 1        | NC       |  |  |

| Diode   | Diode                              | D2/NC | LESD8D3.3CAT5G | 1        | NC       |  |  |

| u1      | Connector                          |       | MOLEX559099872 | 1        |          |  |  |

| T-IC    | Touch IC                           |       | S3601          | 1        |          |  |  |

Table 9.3.2

### 9.3.3 TSP FPC Placement

|     | Table 10.1 |                       |      |        |                                         |  |  |  |

|-----|------------|-----------------------|------|--------|-----------------------------------------|--|--|--|

| No. | Item       | Condition             | Qnty | Result | Judgment Criterion                      |  |  |  |

| 1   | HTS        | 80°C,240hr            | 5 ea | OK     | 1. In the process of the test sample to |  |  |  |

| 2   | LTS        | -40°C,240hr           | 5 ea | OK     | work properly, no dysfunction。          |  |  |  |

| 3   | THS        | 60°C/90%RH,240hr      | 5 ea | OK     | 2. The test is finished, return to room |  |  |  |

| 4   | НТО        | 70°C,240hr            | 5 ea | OK     | temperature, the sample                 |  |  |  |

| 5   | LTO        | -20°C,240hr           | 5 ea | OK     | appearance, display function is         |  |  |  |

| 6   | TST        | -40°C~80°C, 60 Cycles | 5 ea | OK     | normal, no new display abnormal。        |  |  |  |

# 10. Reliability 10.1 Environmental test

# **10.2 Other test**

Table 10.2

| No. | Item |                     | Condition                               | Qnty | Result | Judgment Criterion                                                           |

|-----|------|---------------------|-----------------------------------------|------|--------|------------------------------------------------------------------------------|

| 1   | ESD  | Front on<br>display | ±4KV(Contact)/ ±8kV(Air),<br>150pF/330Ω | 5 ea | ОК     | In the process of<br>the test sample to<br>work properly, no<br>dysfunction。 |

# 11. Handling Precautions 11.1 Mounting Method

The AMOLED panel module consists of two slim glasses with polarizer which can easily get damaged. Since the module is constructed as to be fixed by utilizing fitting holes in the printed circuit board. Extreme care should be used when handling the AMOLED modules.

# **11.2 Caution of AMOLED Handling and Cleaning**

When cleaning the display surface, use soft cloth solvent as recommended below and wipe gently.

- Isopropyl alcohol

- Ethyl alcohol

- Trichlorotriflorothane

Do not wipe the display surface with dry or hard materials that will damage the polarizer surface. Do not use the following solvent.

- Water

- Ketone

- Aromatics

Do not wipe ITO pad area with the dry or hard materials that will damage the ITO patterns. Do not use the following solvent on the pad and prevent it from being contaminated.

- HCFC (Other area except ITO pad can use the HCFC for cleaning process)

- Soldering flux

- Chlorine(Cl), Sulfur(S)

- Spittle, Fingerprint

If the product is not wrapped with a desiccant added pad, ITO pattern can be damaged by corrosion. Good Display suggests wrapping a product with a desiccant unless customers particularly indicate that they do not want it. In case ITO pattern corrodes due to the usage of chlorine, sulfur or customer's mishandling of the product, the responsibility lies with the customer.

### **11.3 Caution against Static Charge**

For AMOLED module, use C-MOS LSI drivers, therefore we recommend that you ; Connect any unused input terminal to VCI or VSS, do not input any signals before power is turned on, and ground your body, work/assembly areas, assembly equipment to protect against static electricity. It could occur static electricity when taping off the film which protects AMOLED. Against static charge, you should make sure that the product is safe or not by experiment in advance.

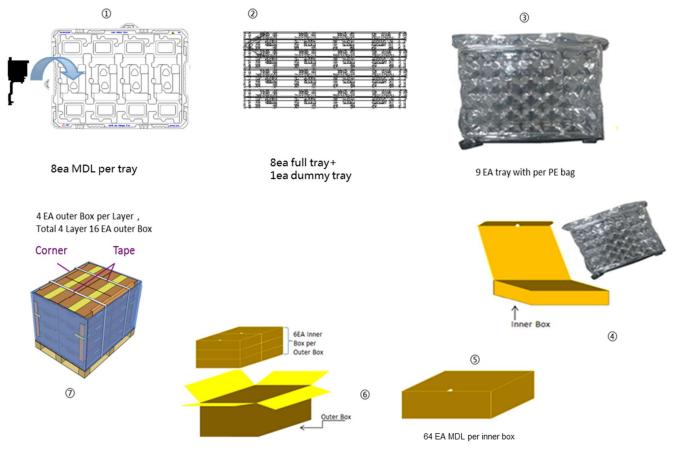

### 11.4 Packing

- The packing principle is that AMOLED module should keep its packing condition at the time of delivery.

- For safety & avoiding the module damage, Carton box must stack the below 4 boxes. When storing the AMOLED after unpacking, note the followings.

- AMOLED module is consisted of GLASS and assemblies. It should avoid pressure, strong impact, and being dropped from a height.

- To prevent modules from degradation, do not operate or store them in a place where they are directly exposed to sunlight or high temperature/humidity.

# **11.5 Caution for Operation**

- If you do not follow normal POWER ON, OFF sequence or abnormal operating, then AMOLED module can be damaged electro-optically and does not recover. Do not change software without Good Display confirmation.

- Response time may extremely delay at a temperature lower than operating range; AMOLED does not normally operate at a high temperature. But this may recover at a proper temperature.

- When you set optimal operating voltage to AMOLED module, you can see the optimal contrast of AMOLED. So, add voltage controllable function at SET Module.

- AMOLED module may not display normally when twisting power or pressing power is added. Therefore you should secure AMOLED module maximum thickness at set assembly not to have any pressure affect AMOLED module.

- Electro-chemical reaction may occur when there is humidity on pad; therefore, you should use AMOLED Module below maximum operating humidity.

- AMOLED Module Power Vdd should be designed to protect surge current at SET Module.

- You should not damage connector and cable for AMOLED module assembly by force folding or by applying extreme power.

- AMOLED may not display normally when it is interfered by surrounding elements, therefore you should consider setting design not to damage AMOLED module by surrounding elements.

- To satisfy EMI standards, you should plan your design after considering emitting energy.

- We cannot guarantee display characteristics outside viewing area, therefore your set window should be fixed into viewing area.

- Image-sticking may occur if AMOLED displays same image for a long time, so you need to make a change for AMOLED.

- When remove the window protective film, necessarily need to apply as a way to prevent Cushion and conductive tape Delamination.

- As an upper Figure, the handler takes off the direction of the arrow to remove the protective film.

# 11.6 Storage

- Place in a dark place where neither exposure to direct sunlight nor any fluorescent light is permitted and keep at room temperature & room humidity.

- Store with no contact with polarizer surface.

[It is recommended to store them as they have been contained in the inner container when we delivered them.

### **11.7 Safety Precautions**

- Disassembly or modification may cause electric shock, damages to sensitive part inside of the AMOLED module, dust adhesion, or scratches on the display part.

- In the event that the contents of AMOLED module are on skin, wipe them with a paper towel or gauge and wash the part well, and receive medical attention if necessary.

- Do not use the AMOLED module for the special purpose besides display units.

- Be careful of the glass chips that may cause injury to fingers of skin, when the display part is broken.

- For keeping safe quality from outer exposure or contamination, modules should be consumed within 2 months after unpacking.

# 12. Packing Specification 12.1 Box Pack

Figure 12.1